§ 24. Логические элементы компьютера

Простейшие элементы

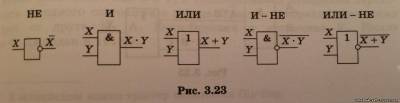

В компьютерах все вычисления производятся с помощью логических элементов — электронных схем, выполняющих логические операции. Обозначения простейших элементов приводятся в таблице на рис. 3.23 (ГОСТ 2.743-91). Заметьте, что небольшой кружок на выходе (или на входе) обозначает операцию «НЕ» (отрицание, инверсию).

Может показаться, что для реализации сложных логических функций нужно много разных видов логических элементов. Однако, как мы видели в § 22, любую логическую функцию можно представить с помощью операций «НЕ», «И» и «ИЛИ» (такой набор элементов называется полным). Именно эта классическая «тройка» используется в книгах по логике, а также во всех языках программирования. Тем не менее инженеры часто предпочитают строить логические схемы на основе элементов «ИЛИ-НЕ». Как показано в § 19, эта функция (штрих Шеффера) позволяет реализовать операции «НЕ», «И» и «ИЛИ», а значит, и любую другую операцию.

Если нужно составить схему по известному логическому выражению, её начинают строить с конца. Находят операцию, которая будет выполняться последней, и ставят на выходе соответствующий логический элемент. Затем повторяют то же самое для сигналов, поступающих на вход этого элемента. В конце концов должны остаться только исходные сигналы — переменные в логическом выражении.

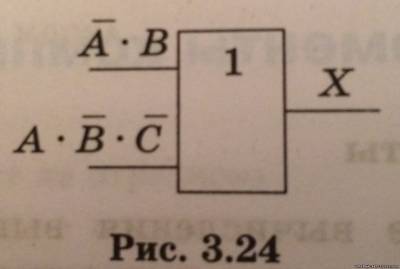

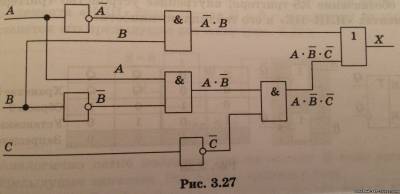

Составим схему, соответствующую выражению

Х=˥А*В+А*˥В*˥С.

Последняя операция — это логическое сложение, поэтому на выходе схемы будет стоять элемент «ИЛИ» (рис. 3.24).

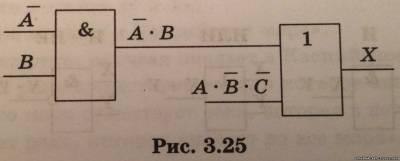

Для того чтобы получить на первом входе ˥А*В, нужно умножить ˥A на В, поэтому добавляем элемент «И» (рис. 3.25).

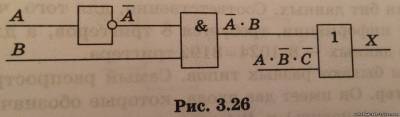

Чтобы получить ˥А, ставим элемент «НЕ» (рис.:3.26).

Аналогично разбираем вторую ветку, которая поступает на второй вход элемента «ИЛИ» (рис. 3.27).

Схема составлена, её входами являются исходные сигналы А, В и С, а выходом — X.

Триггер

Слово «триггер» происходит от английского слова «trigger» — «защёлка» или спусковой крючок. Так называют электронную схему, которая может находиться только в двух состояниях (их можно обозначить как 0 и 1) и способна почти мгновенно переходить из одного состояния в другое. Триггер изобрели независимо друг от друга М. А. Бонч-Бруевич и англичане У. Икклз и Ф. Джордан в 1918 г.

В современных компьютерах на основе триггеров строится быстродействующая оперативная память. Один триггер способен хранить один бит данных. Соответственно, для того, чтобы запомнить 1 байт информации, требуется 8 триггеров, а для хранения 1 килобайта данных — 8*1024 = 8192 триггера.

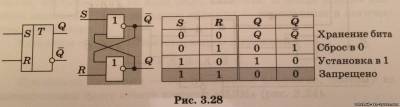

Триггеры бывают разных типов. Самый распространённый — это RS-триггер. Он имеет два входа, которые обозначаются как S (англ. set — установить) и R (англ. reset — сброс), и два выхода — Q и ˥Q, причём выходной сигнал ˥Q является логическим отрицанием сигнала Q (если Q =1, то ˥Q = 0, и наоборот).

RS-триггер можно построить на двух элементах «И-НЕ» или на двух элементах «ИЛИ-НЕ». На рисунке 3.28 показано условное обозначение RS-триггера, внутреннее устройство триггера на элементах «ИЛИ-НЕ» и его таблица истинности.

Триггер использует так называемые обратные связи — сигналы с выходов схем «ИЛИ-НЕ» поступают на вход соседней схемы. Именно это позволяет хранить информацию.

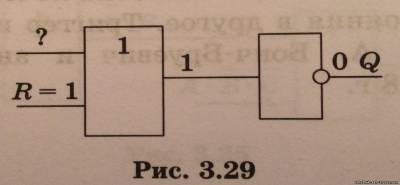

Построим таблицу истинности триггера. Начнем с варианта, когда S= 0 и R = 1. Элемент «ИЛИ-НЕ» в нижней части схемы можно заменить на последовательное соединение элементов «ИЛИ» и «НЕ». Независимо от второго входа, на выходе «ИЛИ» будет 1, а на выходе «НЕ» — ноль. Это значит, что Q = 0 (рис. 3.29).

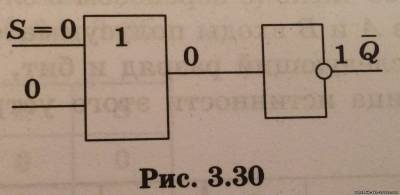

Тогда на входе другого элемента «ИЛИ-НЕ» будут два нуля, а на выходе ˥Q — единица (рис. 3.30).

Поскольку основным выходом считается Q, мы записали в триггер значение 0. Схема симметрична, поэтому легко догадаться, что при S = 1 и R = 0 мы запишем в триггер 1 (Q = 1).

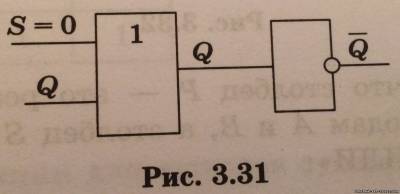

Теперь рассмотрим случай, когда S = 0 и R = 0. На входе первого элемента «ИЛИ» будет сигнал Q + 0 = Q, поэтому на выходе Q останется его предыдущее значение (рис. 3.31).

Аналогично легко показать, что на выходе Q тоже остаётся его предыдущее значение. Это режим хранения бита.

Для случая S=1 и R=1 мы увидим, что оба выхода становятся равны нулю — в этом нет смысла, поэтому такой вариант запрещён.

Для хранения многоразрядных данных триггеры объединяются в единый блок, который называется регистром. Регистры (размером от 8 до 64 битов) используются во всех процессорах для временного хранения промежуточных результатов.

Над регистром, как над единым целым, можно производить ряд стандартных операций: сбрасывать (обнулять), заносить в него код и т. д. Часто регистры способны не просто хранить информацию, но и обрабатывать её. Например, существуют регистры-счётчики, которые подсчитывают количество импульсов, поступающих на вход.

Сумматор

Как следует из названия, сумматор предназначен для сложения (суммирования) двоичных чисел. Сначала рассмотрим более простой элемент, который называют полусумматором. Он выполняет сложение двух битов с учетом того, что в результате может получиться двухразрядное число (с переносом в следующий разряд).

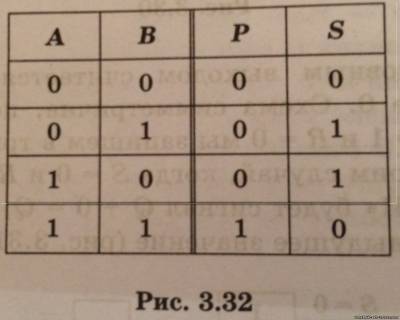

Обозначим через А и В входы полусумматора, а через Р и S — выходы (перенос в следующий разряд и бит, остающийся в текущем разряде). Таблица истинности этого устройства показана на рис. 3.32.

Легко увидеть, что столбец Р — это результат применения операции «И» ко входам A и В, а столбец S — результат операции «исключающее ИЛИ»:

Р=А*В, S = A+B=˥A*B+A*˥B.

Формулу для S можно также записать в таком виде:

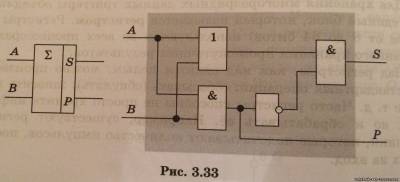

S=˥A*B+A*˥B=(A+B)*(˥A+˥B)=(A+B)*˥(A*B)=(A+B)*˥P,

что позволяет построить полусумматор, используя всего четыре простейших элемента (рис. 3.33).

Слева показано условное обозначение полусумматора, греческая буква Σ здесь (и в математике) обозначает сумму.

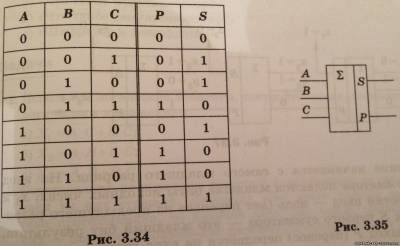

Полный одноразрядный сумматор учитывает также и третий бит С — перенос из предыдущего разряда. Сумматор имеет три входа и два выхода. Таблица истинности и обозначение сумматора показаны на рис. 3.34, 3.35.

Логические функции для выходов сумматора вы можете найти самостоятельно.

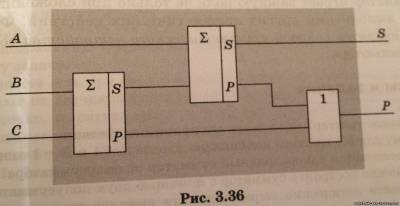

Сумматор можно построить с помощью двух полусумматоров и одного элемента «ИЛИ» (рис. 3.36).

Сначала складываются биты В и С, а затем к результату добавляется бит А. Перенос на выходе сумматора появляется тогда, когда любое из двух промежуточных сложений даёт перенос.

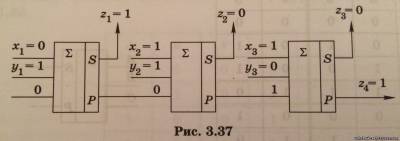

Для сложения многоразрядных чисел сумматоры объединяют в цепочку. При этом выход Р одного сумматора (перенос в следующий разряд) соединяется с входом С следующего. На рисунке 3.37 показано, как складываются два трёхразрядных числа: X =1102 иУ = 0112. Сумма Z = 10012 состоит из четырёх битов, поэтому на выходе последнего сумматора бит переноса будет равен 1.

Сложение начинается с самого младшего разряда. На вход первого сумматора подаются младшие биты исходных чисел, х1 и y1 , а на третий вход — ноль (нет переноса из предыдущего разряда). Выход S первого сумматора — это младший бит результата, z1 а его выход Р (перенос) передаётся на вход второго сумматора и т. д. Выход Р последнего из сумматоров представляет собой дополнительный разряд суммы, т. е. z4.

Сумматор с последовательным переносом, показанный на рис. 3.37, работает слишком медленно. Поэтому в реальных процессорах применяют схемы с ускоренным переносом, которые выполняют сложение намного быстрее, но используют дополнительные логические элементы.

Сумматор играет важную роль не только при сложении чисел, но при выполнении других арифметических действий. Фактически он является основой арифметического устройства современного компьютера.